Consorzio per la Formazione e la Ricerca in Ingegneria dell'Informazione

Politecnico di Milano

XIV Master in Tecnologia dell'Informazione Rapporto finale

# A model for Assembly Instruction Timing and Power Estimation on Superscalar Architectures

Autore: Giovanni Beltrame Tutor: Carlo Brandolese Area: ESD Sponsor: POET Project 1 luglio 2002 Versione: 1.4 Stato: *release*

# Diffusione del documento

La diffusione del presente documento è limitata al Centro CEFRIEL e a POET Project ed è di proprietà del CEFRIEL e di POET Project. Ogni riproduzione da parte di altri soggetti senza esplicita autorizzazione è pertanto vietata a norma delle leggi vigenti.

# Revisioni

| Data           | Versione | Stato   | Commento                               |

|----------------|----------|---------|----------------------------------------|

| 3 marzo 2002   | 0.1      | draft   | Prima stesura                          |

| 6 marzo 2002   | 0.2      | draft   | Corretti e aggiornati i capitoli 1, 2, |

|                |          |         | 3,5                                    |

| 8 marzo 2002   | 0.3      | draft   | Aggiunta del capitolo 4                |

| 11 marzo 2002  | 0.4      | RC1     | Correzioni e bugfix, aggiunta ap-      |

|                |          |         | pendice                                |

| 12 giugno 2002 | 1.1      | draft   | Prima versione del rapporto finale,    |

|                |          |         | aggiunta del capitolo 7                |

| 22 giugno 2002 | 1.3      | RC2     | Aggiornamento risultati e correzioni   |

| 1 luglio 2002  | 1.4      | release | Correzioni stilistiche minori          |

|                |          |         |                                        |

# Table of Contents

| 1 | Intro        | oduction                             | 1  |  |  |  |  |  |

|---|--------------|--------------------------------------|----|--|--|--|--|--|

| 2 | Background 3 |                                      |    |  |  |  |  |  |

|   | 2.1          | System Design                        | 3  |  |  |  |  |  |

|   |              | 2.1.1 Co-Design                      | 4  |  |  |  |  |  |

|   | 2.2          | Power Estimation Techniques          | 5  |  |  |  |  |  |

|   |              | 2.2.1 Transistor-Level Estimation    | 5  |  |  |  |  |  |

|   |              | 2.2.2 Gate-Level Estimation          | 5  |  |  |  |  |  |

|   |              | 2.2.3 RT-level estimation            | 6  |  |  |  |  |  |

|   |              | 2.2.4 Behavioral-Level Estimation    | 6  |  |  |  |  |  |

|   |              | 2.2.5 Architectural-level estimation | 7  |  |  |  |  |  |

|   | 2.3          | Instruction-Level Power Estimation   | 7  |  |  |  |  |  |

|   |              | 2.3.1 The Interlock-Free Model       | 8  |  |  |  |  |  |

|   |              | 2.3.2 The Interlock-Aware Model      | 8  |  |  |  |  |  |

| 3 | Мос          | del Definition                       | 11 |  |  |  |  |  |

|   | 3.1          |                                      | 11 |  |  |  |  |  |

|   | 3.2          |                                      | 12 |  |  |  |  |  |

|   |              |                                      | 12 |  |  |  |  |  |

|   |              |                                      | 12 |  |  |  |  |  |

| 4 | Met          | thodology                            | 17 |  |  |  |  |  |

|   | 4.1          | •                                    | 17 |  |  |  |  |  |

|   | 4.2          |                                      | 18 |  |  |  |  |  |

|   | 4.3          |                                      | 19 |  |  |  |  |  |

|   |              |                                      | 19 |  |  |  |  |  |

|   |              | • • • •                              | 23 |  |  |  |  |  |

|   | 4.4          | <b>.</b>                             | 24 |  |  |  |  |  |

|   | 4.5          | -                                    | 24 |  |  |  |  |  |

| 5 | Soft         | ware Tools                           | 27 |  |  |  |  |  |

|   | 5.1          | Behavioral Simulator                 | 27 |  |  |  |  |  |

|   | 5.2          |                                      | 30 |  |  |  |  |  |

|   | 5.3          |                                      | 32 |  |  |  |  |  |

|   | 5.4          |                                      | 33 |  |  |  |  |  |

|   | 5.5          |                                      | 33 |  |  |  |  |  |

| 6 | Tara         | get Architectures                    | 35 |  |  |  |  |  |

| - | -            |                                      | 35 |  |  |  |  |  |

|   | 0.1          |                                      | 50 |  |  |  |  |  |

|   |      | 6.1.1 Structural Hazards                                 | 35 |

|---|------|----------------------------------------------------------|----|

|   |      | 6.1.2 Data Hazards                                       | 35 |

|   |      | 6.1.3 Control Hazards                                    | 36 |

|   |      | 6.1.4 Dynamic Scheduling                                 | 37 |

|   | 6.2  | Target Architectures                                     | 38 |

|   |      | 6.2.1 Intel486™                                          | 38 |

|   |      | 6.2.2 microSPARC™-II                                     | 43 |

| 7 | Dev  | veloped Simulators                                       | 47 |

|   | 7.1  |                                                          | 47 |

|   |      | 7.1.1 The microSPARC™-II TrIBeS library                  | 47 |

|   |      | 7.1.2 The SparcV8 assembly compiler                      | 52 |

|   |      | 7.1.3 Simulator validation                               | 54 |

|   | 7.2  | Intel486™                                                | 54 |

|   |      | 7.2.1 The Intel486 <sup>TM</sup> TrIBeS library $\ldots$ | 55 |

|   |      | 7.2.2 The 80x86 assembly compiler                        | 55 |

|   |      | 7.2.3 Simulator validation                               | 57 |

| 8 | Exp  | erimental Results                                        | 59 |

| • | 8.1  |                                                          | 59 |

|   | 8.2  |                                                          | 60 |

|   |      |                                                          | 60 |

|   |      |                                                          | 61 |

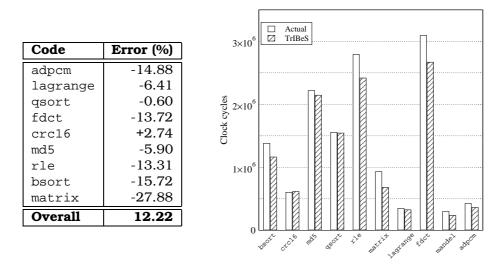

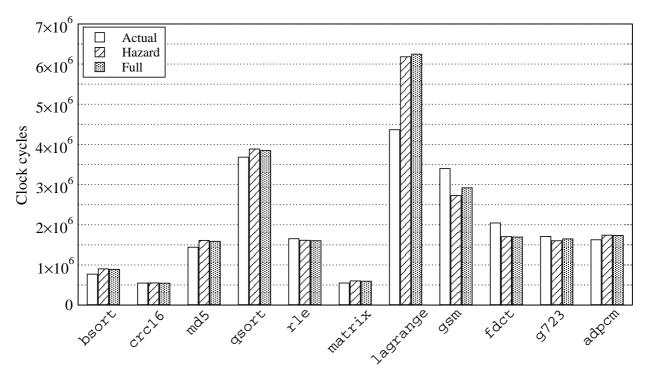

|   | 8.3  | Tuning Results                                           | 62 |

|   |      | 8.3.1 microSPARC™-II                                     | 62 |

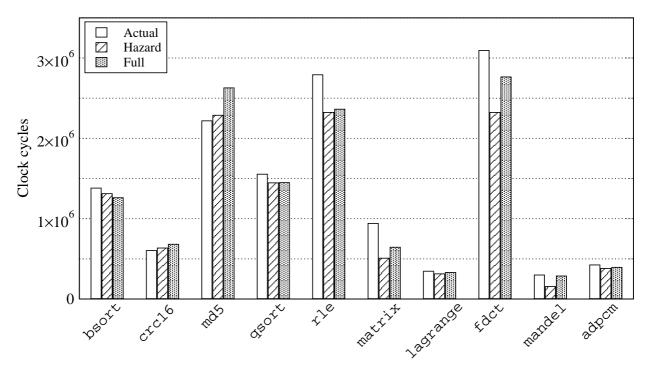

|   |      | 8.3.2 Intel486™                                          | 63 |

|   | 8.4  | Validation Results                                       | 64 |

|   |      | 8.4.1 microSPARC™-II                                     | 65 |

|   |      | 8.4.2 Intel486™                                          | 66 |

|   | 8.5  | Future Work                                              | 67 |

|   | 8.6  |                                                          | 67 |

| A | Used | d Notation                                               | 69 |

| в | Mic  | ro-Instruction Templates                                 | 71 |

| D | B.1  | •                                                        | 71 |

|   | 0.1  |                                                          | 71 |

|   |      |                                                          | 72 |

|   |      |                                                          | 73 |

|   |      |                                                          | 74 |

|   |      |                                                          | 74 |

|   | B.2  | -                                                        | 75 |

|   |      | B.2.1 Integer ALU Instructions                           | 75 |

| B.2.2 | Control Transfer Instructions | 76 |

|-------|-------------------------------|----|

| B.2.3 | Floating Point Instructions   | 76 |

# 1 Introduction

Today we are facing an increasing market for embedded applications: therefore there is a stronger need to obtain design solutions that would concurrently meet time-to-market, low cost and flexibility. In order to obtain such solutions, the increasing relevance of power consumption in modern embedded applications demands tools to predict with reasonable confidence the power consumption both for hardware and software. While in literature the power estimation for hardware is well established, methodologies for software still require some further insight.

The aim of this work is to provide a simple and accurate static time and energy consumption model for micro-processor instruction sets. In particular, the novelty of this works stand in the introduction of the support of execution parallelism in the temporal and energy estimation process.

Most of today's embedded devices are heterogeneous systems composed of dedicated ICs, memories, A/D and D/A converters, sensors and microprocessor cores. In the past decade, a considerable research effort has been made to study the power behavior of digital systems and of specific components such as memories, leading to a firm ground on which EDA vendors have developed efficient and reliable tools. With the increasing request of complex functionalities, the amount of software composing embedded systems has rapidly grown, making the microprocessor and the software itself highly critical portions of the design.

Optimal embedded power savings result from an integrated hardware-software design methodology that focuses on the power dissipation problem, starting from the very early phases of the design process. One of the primary power-saving techniques to investigate is a lower supply voltage. Halving the supply voltage reduces static power dissipation to one fourth. However, a reduced supply voltage, along with today's fast clocks, produce noise-immunity problems. Another possible problem with a lower supply voltage is the limited availability of logic functions, that are usually essential to determine the success of a product.

Processor selection is the first step for low power design. A possible approach might be to select fast and powerful processors, relying on plenty of computing power in order to run complex programs. A wiser solution would be to select a lower speed processor with just enough capability for the application. The practical answer lies somewhere between these two approaches and depends on the power-management flexibility of the chosen processor.

System power consumption also directly relates to the processor clock speed. Many microprocessors support a variable-speed clock, allowing designers to adjust the frequency for optimal power savings and to retain the capability for extra speed when an application requires it. The program can increase the CPU clock speed when processing demands are high and then go back to a lower speed for non-critical tasks. This type of dynamic control is quite effective in battery-operated systems.

Intel, Microsoft, and Toshiba America Information Systems introduced an Advanced Configuration and Power Interface (ACPI) for desktop and notebook PCs in 1997. ACPI transfers the responsibility for power management from the firmware to the operating system. ACPI defines a series of reduced-power states for the system, processor, and peripheral devices. When the system has been idle for a specified amount of time, the software enters system power-management states, also called sleep states. The CPU does no work in any of the sleep states. The ACPI specification defines four levels of sleep states, each with increased power savings but requiring more time to resume.

Although ACPI targets desktops and notebooks, it might be an interesting model to follow when developing a power-management software for embedded systems. Not all applications, though, can afford the overhead of such a software. Often, the only way to optimize software power dissipation is to measure the energy consumption in real time as the application program executes in the embedded hardware platform. Then, a designer can either rewrite or optimize the most power-demanding routines or implement them in dedicated hardware. This approach falls in the class of the co-design methodologies, i.e. the concurrent design of both the hardware components and the software functions. In such a framework it is essential to delay as much as possible all the decisions concerning the target technology in order to evaluate many different alternatives.

The work presented here analyses the power related issues that arise when designing heterogeneous embedded systems concurrently. In particular it focuses on questions related to software power consumption evaluation, at the highest granularity level. The system to be modeled is usually described by means of a high-level language that captures the functional behavior while neglecting all the implementations and technology-dependent characteristics. A modification to the system when the different components have already been committed to the target technology may have a significant impact on the design times and costs. Furthermore, the sooner optimizations are performed, the more their effect is valuable. A simplistic explanation of this well-known fact is that at the beginning of the design cycle, all degrees of freedom can be exploited, while at later phases, when many decisions have already been taken, only a few alternatives are available to designers, possibly leading to modest enhancements.

Two phases are crucial, and relatively unexplored, in the co-design flow: system partitioning and model verification. Partitioning is the task of assigning each of the functionalities or modules to a specific partition, i.e. hardware or software. The assignment of functions to partitions is a NP-complete problem and is thus often solved heuristically. The three ingredients for a good solution are an efficient algorithm, a well-structured cost function and accurate models to estimate the characteristics of the different modules.

While a number of extremely efficient algorithms have been proposed in literature and a solid background exists about cost-functions, estimation models are still a big issue. This is basically due to the fact that an estimation model, to be considered acceptable and to be adopted, must meet some criteria such as accuracy, stability and computational efficiency. Most of all, a viable estimation technique must operate on a high-level description of the system so that no implementation decision needs to be committed prior to partitioning.

The second critical point in any hardware/software co-design flow is model verification. This can be done with two main purposes: functional verification and timing, or power, verification. In the former case a simulator for the high-level language is sufficient. In the latter case, however, simulation alone is not enough since execution times, or power consumptions, should also be checked. When simulating heterogeneous systems the main issue to be dealt with is synchronization. This implies the notion of a global, real time in which the system evolves according to the execution times of the composing processes or instructions. To determine the time duration of each process, again, an accurate estimation technique is necessary. Static figures, computed off-line, are then combined, during simulation, with the dynamical aspects of execution. Neglecting the dynamic effects, the basis for validation also is constituted by a static model of the power consumption.

This work considers the highest level of granularity of the co-design flow, and focuses in particular on power consumption and timing estimations. In this work previous models are extended in order to consider parallel execution of instruction, which is a typical characteristic of current superscalar microprocessors. The proposed model is founded on a theoretical analysis of the estimation problem and on the experimental results that have been obtained by using a set of tools, developed on purpose.

The report is organized as follows: chapter 2 summarizes some of the most interesting results obtained in the past few years on hardware and software power estimation. In chapter 3 a mathematical model for inter-instruction effects and parallel execution issues is introduced: this model is used for the statistical analysis and prediction of execution overheads and of parallel execution factors that influence the timing estimation. Chapter 4 introduces and details the application methodology associated with the model and chapter 5 the software tools developed on purpose to apply such methodology. Finally, chapter 8 describes the experimental setup, and the results of the validation process are presented.

# 2 Background

The increased use of portable applications has placed severe limitations on the power consumed by processors and systems. Energy efficient designs are now just as important as fast and high performance ones. Designing systems to operate longer on a single battery charge is an important consideration in the design of today's portable systems. However, the electronic integration technology cannot help much in power saving issues, while code and architectural optimization can significantly reduce power consumption. Therefore, many researchers have considered power minimization through the modification of the architecture, the high level software and the algorithms. This however will be more effective if a realistic power model for a microprocessor core, its instruction set and the various types of memory accesses were developed. In the following, Section 2.1 briefly describes a typical system design flow; Sections 2.2 describes the main classes of power estimation approaches, working at hardware and software level. Finally, Section 2.3 will detail a different approach: the instruction-level power modeling, which takes into account also architectural issues.

# 2.1 System Design

A typical hardware design flow is structured in a number of steps, each giving a different view of the system. The views differ with respect to two main aspects: the description language or formalism and the level of detail. The following scheme summarizes the foremost characteristics of the different views and gives an outline of a typical industrial design flow.

- **Architectural or System level.** At this level the system is represented as an abstract network of interconnected functionalities. The functionalities are typically modeled as black-boxes whose interface only is known. This representation captures in synthetic and compact way the behavior of the system but does not give any detail on the internal implementation. A rather wide spectrum of formalisms is used to capture such a description of a system: graphical models [9, 23] (often invented ad-hoc by CAD or EDA vendors), different flavors of Petri Nets [15], CSP (Communicating Sequential Processes), State Charts [32, 31], or extension to the C/C++ languages such as Hardware C [14] and SystemC [1].

- **Behavioral level.** The architectural level description is converted into a functionally equivalent behavioral description. This process is currently performed manually by the design team, in some cases with the support of commercial co-design tools. The behavioral view adds an algorithmic description of the functionalities of the system. The language used to describe a system at this level is typically VHDL, but recently SystemC is gaining more and more popularity. Although such a description gives much more details on the internal structure of the functional blocks of the system, the notions of time, i.e. clock, and availability of hardware resources are not present yet.

- **Register-transfer level.** From the behavioral description of system and a set of constraints, a register-transfer model can be derived. The constraints typically specify the timing requirements and the resources availability. Both are used to drive and control automatic tools (behavioral synthesis tools such as Behavioral Compiler by Synopsys). These tools are cutting-edge technologies and often still require the human intervention. The result of behavioral compilation is a description of the system in terms of purely combinational logic and registers. The languages used are either a subset of the VHDL, usually referred to as RTL-VHDL, or Verilog. At this level of abstraction, data computation is expressed by means of high-level operators such as adders, multipliers, multiplexers and many others operating on compound data types (buses, records, etc.). Registers are described using

specific language templates. The clock signal is introduced explicitly and hardware resources are allocated and bound to the symbolic operators according to the specified constraints. The recently introduced SystemC version 1.1 can describe systems at RT level. The register-transfer view, though sufficiently detailed, still ignores the internal structure of the operators.

- **Gate level.** The register-transfer description is then translated into a gate level model by means of automatic logic synthesis tools (such as Design Compiler and FPGA Express by Synopsys or Galileo and Leonardo by Exemplar Logic). The result is a netlist where operators are expanded into logic gates and compound signals are substituted by sets of single nets. Subsets of the VHDL and Verilog languages, referred to as structural VHDL or Verilog, are often used to describe netlists. Other standard formats such as EDIF (Electronic Design Interchange Format), XNF (Xilinx Netlist Format), blif (Berkeley Logic Interchange Format) are also used. The gates used in the netlist may either be taken from a fictitious technology library or from a commercial library. In the latter case, each component is characterized in terms of delay and capacitance and this allows rather accurate estimates to be performed. Nevertheless, these models are lumped and the simulation is in the discrete time and considers logical values for the signals rather than actual voltage levels. Furthermore, interconnections are characterized using statistical wire-load models since no information is available on the relative geometrical positioning of the gates.

- **Transistor level.** The gate-level netlist is usually given to a silicon foundry where the last steps of the design flow are performed. In particular, each gate or basic component is substituted with its corresponding transistor-level circuit, according to the specific library and technology used. The resulting representation is extremely accurate and details both the actual layout of the cells and the position and length of the interconnections. Combining geometrical information with physical details of the cells and the nets an accurate model can be derived and simulated to obtain a precise characterization, in terms of timing and power consumption.

These steps are typical of most design flows and refer to the realization of application-specific integrated circuits (ASICs) as well as microprocessor and microcontroller cores.

## 2.1.1 Co-Design

Concurrent development of hardware and software is progressively displacing the traditional sequential design. It is becoming common practice to begin the hardware and software design before the system architecture is finalized.

In the design practice, system architects define an architecture consisting of cooperating hardware and software *functions* that form the basis for the actual components design. One major problem of this approach is the definition, design and synthesis of the interfaces, that usually requires a tight cooperation of distinct design groups. Another drawback of such a design paradigm is that a change in the requirements implies a modification in the overall architecture that is often driven by a cost prediction (in terms of area, timing or power) done on the basis of the expertise of system architects.

Another big issues that must be addressed when considering separate design flows for hardware and software is the problem of maintaining permanent control over consistency and correctness. This problem becomes more complex with increasing levels of detail.

This brief outline of the design scenario of typical mixed hardware and software embedded systems highlights the need of a unified approach to the problem.

The co-design flow can be thought of as a sequence of the following steps:

**Specification.** The requirements are translated from an informal language into a formal description of the functionalities. This step should be independent of the target architecture that will be chosen.

- **Simulation.** The formal specification is simulated to verify its functional correctness. It is often required to have a very detailed view of the system and thus accurate models are necessary.

- **Partitioning.** The functionalities composing the system are partitioned, i.e. assigned either to the software or hardware options. In the current practice this step is performed manually by expert designers or system architects.

- **Synthesis.** The hardware and software specifications are translated into their final form, typically a technology netlist for the hardware and an assembly code for the software. These tasks are usually performed using third party commercial tools.

- **Verification.** The low-level models are simulated with a higher level of detail. At this stage, area, time and power figures are known and can be used to derive the exact characteristics of the complete system.

For a number of reasons, such as changes in the requirements or wrong choices performed during the partitioning phase, it is often necessary to evaluate different partitioning alternatives. To limit the design turn-around time it is thus essential to provide a framework that facilitates moving portions of the design from a partition to another. This, in turns, calls for accurate estimation metrics that allow designers to repeat the actual synthesis and verification steps.

## 2.2 Power Estimation Techniques

The assignment of functions to partitions is a NP-complete problem and is thus often solved heuristically. The three ingredients for a good solution are an efficient algorithm, a wellstructured cost function and accurate models to estimate the characteristics of the different modules.

While a number of extremely efficient algorithms have been proposed in literature and a solid background exists about cost-functions, estimation models are still a big issue. Statistical power models have been proposed: they are simulation-based and the activity factors are computed over typical input streams.

Different levels of abstraction can be adopted in estimating the power consumption of a given design; these are described in the following subsections.

### 2.2.1 Transistor-Level Estimation

It is based on the representation of a microprocessor in terms of transistors and nets: this representation is extremely complex and rarely feasible. Furthermore, a transistor-level view of the system uses components models based on linearized differential equations and works in the continuous-time domain<sup>1</sup>. This implies that a simulation of more than one million transistors, even for few clock cycles, requires times that are usually not affordable and anyway not practical for the high-level power characterization. Nevertheless these techniques are extremely valuable as a replacement for physical measurement. Measuring the power consumption of a microprocessor, in fact, requires sophisticated and costly instruments and an electrical modification of the board hosting the microprocessor core in order to have access to the power supply pins. Both these problems often prevent any measurement to be actually performed.

## 2.2.2 Gate-Level Estimation

Methods to estimate the power consumption based on gate-level descriptions of microprocessors or micro-controller cores have been proposed in literature. The main advantage of such methods

$<sup>^{1}</sup>$ The time is actually discrete due to the finite precision of the computer representation of floating point numbers.

with respect to transistor-level simulation approaches is that the simulation is event-driven and takes place in a discrete-time domain, leading to a considerable reduction of the computational complexity, without a significant loss of accuracy. The main shortcoming of such an approach lays in the computational requirements of gate-level simulation. To overcome effectiveness limitations, solutions based on a statistical analysis of the design properties have been proposed in literature. These approaches can be classified in two main groups: static methods and dynamic methods. To the former class belong the techniques presented in [22], [21] and [11]. These methods rely on statistical information (such as the mean activity of the input signals and their correlations) about the input stream to estimate the switching activity of the internal nodes of the circuit. The methods classified in the latter group are aimed at achieving a high level of accuracy at the cost of longer run-times, and are thus unpractical for the microprocessor power-characterization problem.

## 2.2.3 RT-level estimation

A design described at *Register Transfer* (RT) level can be seen as a collection of blocks and a network of interconnections. The blocks, sometimes referred to as macros, are adders, registers, multiplexers etc., while the interconnections are simply nets or group of nets. An assumption underlying the great majority of the approaches presented in literature is that the power properties of a block can be derived from an analysis of the block *isolated* from a design, under controlled operating conditions. The main factor influencing the power consumption model of a macro is the input statistic: if the probabilistic distribution of the inputs is a good approximation of the typical operating conditions of the block, then the power consumption is considered almost independent of the boundary (electrical) conditions. Under this assumption, common macros can be characterized.

To combine the information available for each block into a complete power model for a given design, two further issues must be addressed, two problems arise: the characterization of the interconnections and the higher-level probabilistic description of the system. The former problem derives from the gap between the degree of detail available at layout-level (exact position, shape and length of the wires) and the lack of predictability on the final geometry at RT level. Statistical models have been derived to fill this gap, the most popular being the so-called *wire-load models*, extensively used in commercial synthesis tools. The latter issue has been addressed from different sides and a number of approaches have been proposed in the scientific literature.

### 2.2.4 Behavioral-Level Estimation

A behavioral model is usually provided by means of a high-level hardware description language such as VHDL, Verilog or some flavor of state charts and then translated into an intermediate internal representation typically based on *Control Data Flow Graphs* (CDFGs), where operators are represented by the nodes of the graph while functional dependencies are rendered with arcs. The purpose of behavioral synthesis is to translate such a CDFG into a more detailed, lower-level model. This is done by mapping operators to the available hardware resources (allocation and binding) and by deciding the order of execution of the different operations (scheduling). Binding, allocation and scheduling algorithms are designed to minimize some sort of cost metric while respecting constraints imposed on other metrics. Behavioral power estimation, in this context, is used either as an additional metric to be possibly minimized or as a synthesis constraint.

When analyzing the power consumption of a complex system, the problem can be split in three sub-problems: first of all, for each unit time interval, determine which units of the system are active, on the basis of the assembly instruction being executed; then, determine a model for the power consumption of the finite state machines implementing the control unit; finally, determine a model for the power consumption of each unit of the system with a sufficiently fine grain and an acceptable accuracy. In this context, a functional unit is a sub-circuit performing a complete operation at a given level of abstraction. The level at which behavioral power estimation operates is usually that of *library macros* (i.e. units performing atomic operations), leaving to a higher

level analysis methodology the task of identifying the interactions and activation intervals of the macros.

## 2.2.5 Architectural-level estimation

The most abstract representation of a complex system, such as a microprocessor, is that at the architectural level. Such a model gives a view composed of a number of interconnected functional blocks, each one devoted to a specific and, in a sense, atomic functionality. In particular, the simplest model of a microprocessor is structured in two interacting units: a control unit and a data-path. The data-path is constituted by a number of arithmetic operators having a rather regular structure and a variable sized register file. This fact allows the adoption of constructive approaches for the power prediction, based on the knowledge of the elementary components constituting the different units. It is also possible to abstract from the internal structure of the functional blocks and perform a black-box analysis based on the input and output switching activities. These activities can be either calculated or estimated using ad-hoc software simulators. The analysis of control units, i.e. complex finite state machines, is much more complex for a twofold reason: their logical structure, in fact, is not regular and hardly predictable, furthermore, their implementation can vary in a spectrum of solutions ranging from PLA solutions to completely random logic implementations.

# 2.3 Instruction-Level Power Estimation

The power estimation methods described in the preceding sections exhibit a number of problems related either to the lack of details (gate-level models) of the microprocessor or to the unpractical time requirements or to both. To overcome these problems, instruction-level measurementbased models have been proposed [29][28][26]. The key point lays in measuring the current drawn by the processor as it executes a long sequence of the same instruction and considering the average current absorbed as representative of such an instruction. This procedure has to be repeated for all instructions to completely characterize the microprocessor model. In this way, a table of the currents drawn by each instruction in the Instruction Set of a given processor is obtained, knowing *a-priori* how many cycles each instruction will take, in a sort of stall-free analysis. To these measured base costs, Malik et al. propose to add a measured stall cost and cache miss cost to each basic block of code. This overhead cost is experimentally measured for each type of stall, and the same activity has to be performed for cache misses. This methodology, although generally applicable to any processor, is not viable: the measures have to be taken for every processor, and the information obtained for one processor cannot be used for estimating values for other processors. In fact, to model an alternative CPU core, a new costly analysis of the entire instruction set has to be carried out. Furthermore, the confidence of the estimations is also seldom considered under a formal viewpoint: the statistical significance of the model of consumption is usually neither considered nor justified.

In 1998, Ramalingam and Schindler proposed an instruction level power model that considered dynamic effects [24]. Their model is based on [29][30] but obtains a more precise estimate for base costs. What the authors actually did is to separate instructions with the same opcode but different addressing modes and to add a statistical analysis of cache and pipeline interlock overheads. But this is anyway not general, in the sense that this methodology needs measures for every processor it has to be applied to.

Another approach has been introduced to overcome the above mentioned limitations, proposing a general methodology, independent of the specific processor, allowing to accurately estimate the energy of an instruction set. The methodology abstracts from the architectural level and focuses on the *functionalities* involved in instruction execution [3]. The resulting functional model exhibits generalization capabilities and allows covering a broad range of 32-bits microprocessors architectures. The energy consumption of each instruction is obtained as linear combination of independent contributions corresponding to a set of disjoint functionalities. The methodology allows an early *virtual* prototyping of the software-bound section of embedded applications on different target processors. In section 2.3.1 the first methodology model is described: it has to be considered a basis from which to start building a more general framework. The analysis of inter-instruction effects is here missing and have been introduced in [2]: the extended model refers in particular to pipelined architectures and does not takes into account the effects related to memory access. The present work represent a step towards the extension of this approach to a general framework that includes parallel instruction execution and memory effects analysis (see chapter 3).

### 2.3.1 The Interlock-Free Model

As mentioned above, the approach proposed in [3] abstracts from the architectural level by determining a set of *functionalities* and by decomposing the computational activity of each instruction in terms of these functionalities. The model provides a *static* estimation of the energy consumption of single instructions. According to [3], the energy dissipation  $e_s$  of an instruction *s* is evaluated as:

$$e_s = \sum_{j=0}^5 e_{s,j} = \left[\sum_{j=0}^5 i f_j \cdot a_{s,j}\right] \cdot V_{dd} \cdot \tau$$

(2.1)

where  $if_j$  is the average current associated with the *j*-th functionality,  $V_{dd}$  is the power supply voltage,  $\tau$  is the clock period and  $a_{s,j}$  is a coefficient expressing the execution time spent by instruction *s* in the *j*-th functionality. The coefficients  $a_{s,j}$  satisfy the following relation:

$$\sum_{j=0}^{5} a_{s,j} = \operatorname{CPI}_{s,\operatorname{nominal}}$$

(2.2)

stating that the time —expressed in clock cycles— spent by instruction *s* in all the functionalities corresponds to its average CPI (*Clock-cycles Per Instruction*) [12]. According to this model the energy absorbed by each instruction is computed as the weighted sum of the contributions of the functionalities. A tuning phase, based on a limited set of experimental data, allows associating to each functionality an average current absorption per clock cycle. It is worth noting that the overall energy consumption is strongly dependent on the number of cycles taken for the execution of assembly instructions. In [3] the timing is assumed to coincide with the nominal value reported in the processor data-sheets. This timing data, being purely static, is a sound starting point for a general energy model but disregards the delays introduced by the interlocks arising from a pipelined execution of the code.

### 2.3.2 The Interlock-Aware Model

The interlock-aware model, presented in [2], is capable of describing timing overheads due to inter-instruction effects in a formal and general way, thus addressing the limitation of the previous approach. The advantages of a *static* model with respect to a dynamic, simulation-based, approach are evident: model application is extremely fast, less complex and less memory intensive. This approach is based on a dynamic characterization —to be performed once and for all— of a given instruction set aimed at producing statically usable figures.

This model focuses on inter-instruction effects related to pipelined execution. In pipelined processors instructions are executed with partial time overlap in order to minimize the average CPI. However, this execution scheme leads to some *hazard* conditions that have to be suitably managed in order to maintain the semantics of the original program. In some cases, it is necessary to stall the pipeline, consequently increasing the nominal CPI. The introduced overhead brings to an increase of the energy consumption that cannot be ignored [24]. According to these

observations, equation (2.1) can be extended by explicitly adding the overhead  $oh_{s,j}$ , yielding:

$$e_s = \left[\sum_{j=0}^5 if_j \cdot (a_{s,j} + oh_{s,j})\right] \cdot V_{dd} \cdot \tau$$

(2.3)

where  $oh_{s,j}$  is a statistical coefficient expressing the execution time spent by instruction *s* in the *j*-th functionality in a stall situation. According to equation (2.3), the actual execution time of instruction *s* is:

$$CPI_{s,est} = \sum_{j=0}^{3} (a_{s,j} + oh_{s,j})$$

(2.4)

Since inter-instruction effects such as pipeline interlocks and cache misses are intrinsically *dynamic events*, a purely static analysis would lead to an oversimplification of the problem. Nevertheless, a static analysis is still viable if a characterization of the dynamic effects is available. Such information can be extracted once for each microprocessor considered and stored in a library. This approach is thus based on a dynamic analysis of the whole instruction set aimed at a statistical characterization whose results, i.e. the  $CPI_{s,est}$ , can then be statically used for the estimation process.

The limitation of this approach becomes evident when parallel execution of instruction and memory related stalls have to be introduced. Most of the modern microprocessors implement a superscalar architecture, thus a model based on a single pipeline is not sufficient to capture the dynamics of such instruction execution. Starting from this observation, the present work extends the previous model in order to overcome this problem, as Chapter 3 details.

# **3 Model Definition**

This chapter introduces the main issues related to the introduction of parallel execution in the methodology described in Section 2.3. Section 3.1 describes the problems related to the mathematical model adopted in the previous works and section 3.2 will extend the model in order to overcome these problems.

## 3.1 **Problem Definition**

The basic assumption made in [3] and maintained in [2] concerns the *a-priori* knowledge of instruction CPIs. Thus, the interlock-free timing of a code portion can be easily obtained by simply summing the CPIs of all the executed instructions. The interlock-aware timing can be obtained in a similar way: a statistical term representing the stall overhead associated to a single instruction is estimated (see Section 2.3.2) and the resulting CPIs can be finally summed up. Given an instruction s, its static stall overhead has to be obtained carefully averaging the contribution deriving from the *dynamic* interaction of s with all possible tuples of instructions, in order to obtain a reliable value. If parallel execution is considered, the actual CPI of an instruction is deeply influenced: if an instruction can be executed in parallel with other instructions, the global CPI decreases and consequently also the instruction actual CPI. In superscalar architectures, the parallel execution of assembly instructions strongly influences both the actual CPI of an instruction and the number and type of possible interlocks. For example, when the three instructions  $s_1$ ,  $s_2$  and  $s_3$  are executed in an ideal pipeline the resulting CPI is 1.0 for all of them. In a superscalar architecture with three ideal pipelines in parallel, the resulting CPI would be 1/3. However, real processors significantly differ from ideal architectures and only a portion of the theoretical parallelism can be exploited. To account for such deviation, a parallelism coefficient has been introduced and defined according to a statistical analysis of the execution of real-world programs on a given architecture. Indicating with n(s) and oh(s) the number of clock cycles for nominal execution and the number of stall cycles of instruction s and with p(s) the parallelism coefficient, the estimated CPI is expressed as:

$$CPI_{est}(s) = p(s) \cdot [n(s) + oh(s)]$$

(3.1)

Considering the functionality decomposition, this equation becomes:

$$CPI_{est}(s) = \sum_{j=0}^{4} p(s) \cdot [n(s,j) + oh(s,j)]$$

(3.2)

where p(s) is a statistical factor representing the parallelism that can be exploited executing instruction s with respect to the whole instruction set, while n(s,j) and oh(s,j) are latency values associated to instruction s and the j-th functionality, corresponding to the coefficients  $a_{s,j}$  and  $a'_{s,j}$  of equation (2.4). On the contrary, the energy associated to each instruction is still described by equation (2.3), because energy is an additive quantity, so it is not reduced by the parallel execution. However, it has to be noticed that the reduction of the actual CPI given by equation (3.1) implies that the average power w(s) absorbed by each instruction is increased with the the parallel execution, the mean power w(s) being given by the following equation:

$$w(s) = \frac{e(s)}{CPI_{est}(s) \cdot \tau}$$

(3.3)

where  $\tau$  is the clock period.

The newly introduced parameter  $p_s$  is associated to a single instruction, so it can be used statically in a time or power estimation process. However, it is obtained by folding the *dynamic*

information about the parallel instruction execution on the only instruction s in a way similar to what has been done for the coefficient  $oh_{s,j}$ . The methodology that lead to the estimation of these parameters is described in the following section.

# 3.2 Mathematical Model

For the purpose of producing a static estimation of the actual CPI associated to a given instruction, a taxonomy of instruction sets has been proposed. This taxonomy is essential to reduce model complexity and to allow for a feasible statistical analysis. Starting from such a taxonomy, a mathematical model is introduced with the purpose of estimating the overhead caused by inter-instruction effects and the coefficient related to parallel execution.

## 3.2.1 Instruction Set Taxonomy

In order to maintain the approach as general as possible, no specific architecture or set of architectures should be considered. This is due to the fact that each architecture is characterized by strongly different execution capabilities; choosing one of them thus would lead to a closed, non-extensible model.

A simple solution to this issue is to provide some general classes to be associated with architecture-specific instructions. Recalling what has been done in [2], instruction classes were associated to the type of hazard their members could cause, in order to classify instruction with respect to their dynamic behavior. Having introduced parallelism, the classification must take care of the dynamic interaction between instruction with respect to both inter-instruction effects and parallel execution, as formalized by the following definition.

**Definition 1** Given an instruction set  $\mathcal{I}$ , the equivalence relation  $\mathcal{R} \subseteq \mathcal{I} \times \mathcal{I}$ :

$s_i \mathcal{R} s_j \iff s_i$  and  $s_j$  have similar dynamic behavior;

defines a taxonomy  $C \in 2^{\mathcal{I}}$  on the instruction set  $\mathcal{I}$  as the partition induced by  $\mathcal{R}$  on the instruction set  $\mathcal{I}$ . The cardinality |C| of the taxonomy depends on the relation  $\mathcal{R}$ . The taxonomy C is thus formed by the classes  $c_i$  with  $i \in [1; |C|]$ .

Definition 1 gives a way to obtain the taxonomy based on the equivalence relation  $\mathcal{R}$ . Nevertheless,  $\mathcal{R}$  is still to be properly defined for each instruction set and architecture. Definition 1 gives a way to obtain the taxonomy based

on the equivalence relation  $\mathcal R.$  Three approaches are possible:

- **Architectural** The relation  $\mathcal{R}$  is defined *a priori* and is based on the knowledge of both the instruction set and the architectural details.

- **Numerical** The relation  $\mathcal{R}$  is defined *a posteriori* based on the data extracted from simulation of the dynamic behavior of instructions.

- $\label{eq:Full} \begin{tabular}{ll} \begin{tabular}{ll} The relation $\mathcal{R}$ is always false. In this case each instruction belongs to a different case, i.e. no classification is performed. \end{tabular}$

Chapter 8 shows and discusses the results obtained using these classifications.

### 3.2.2 Model Definition

A statistical characterization of the instruction timing can be obtained from equation (3.2). It is thus necessary to statistically characterize the overhead parameter oh(s, j) and the parallelism coefficient p(s). However, to estimate the instruction timing, it is sufficient to know the global overhead associated to each instruction, that is the parameter  $oh(s) = \sum_{j=0}^{4} oh(s, j)$ . The overhead per functionality can be obtained from this global value as described in [3].

### 3.2.2.1 Interlock model

As an extension of the approach described in [2], this work uses some definitions that are briefly recalled here. An *execution trace*  $\Gamma$  can be seen as an ordered set of instructions executed during a program run. Let a trace  $\Gamma$  be:

$$\Gamma = \{\gamma_1, \gamma_2, \dots, \gamma_N\}, \quad \gamma_k \in I, \quad N > 0$$

where N indicates the execution trace size. Instructions  $\gamma_k$  are then classified by means of the relation  $\mathcal{R}$  and the *membership function* is accordingly:

$$\langle k,i\rangle = \begin{cases} 1 & \text{if } \gamma_k \in c_i \\ 0 & \text{otherwise} \end{cases}$$

where the membership function shows the following property:

$$\sum_{i=0}^{\mathcal{C}} \langle k, i \rangle = 1 \tag{3.4}$$

since an instruction belongs to one and only one class of a partition.

The overhead introduced by dynamic effects during the execution can be associated to the instruction that has been stalled in order to resolve an hazard situation. This is described by the following definition:

**Definition 2** The delay introduced with respect to instruction  $\gamma_k$  is given by the function  $t(\gamma_k)$ .

The function  $t(\gamma_k)$  represents the overhead associated to instruction  $\gamma_k$ ; such overheads have to be collected and associated to instruction classes. Given the probability of finding a class in the execution trace, it is possible to define a stochastic variable associated to it:

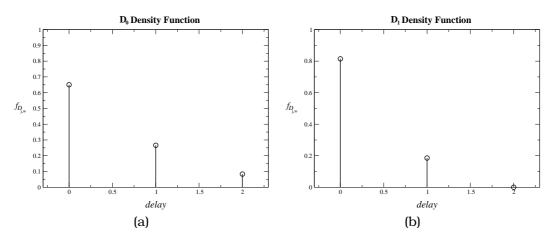

**Definition 3** The class delay is the delay associated with the execution of an instruction belonging to class  $c_i$  when interacting with some other instruction; it is modeled by the stochastic variable  $D_i$ , which is characterized by its density function:

$$f_{D_i}(d) = \frac{\sum_{k=1}^N \delta_{t(\gamma_k)=d} \langle k, i \rangle}{\sum_{k=1}^N \langle k, i \rangle}$$

(3.5)

where N is suitably large<sup>1</sup>.

The overhead parameter oh(s) can be obtained directly from the class delay: it is sufficient to know the instruction class c associated to instruction s, and then average the corresponding stochastic variable.

#### 3.2.2.2 Parallel Execution Model

The parallelism coefficient can be estimated experimentally starting from the execution trace  $\Gamma$  and observing the instructions that are executed in parallel. Similarly to the computation of overheads, the parallelism coefficients are referred to instruction classes. According to this approach, the more instructions  $s \in c_i$  belonging to a given class are executed in parallel, the lower the corresponding parallelism coefficient p(s) and  $CPI_{est}(s)$  are. To determine p(s) it is necessary to know when an instruction  $\gamma_k$  starts and ends executing. The notion of time is here intended as the number of clock cycles since the beginning of the execution. This is clarified by the following definition.

<sup>&</sup>lt;sup>1</sup>For a good approximation,  $N \ge 10^6$ .

**Definition 4** Let  $t_{in}(\gamma_k)$  the starting time of a generic instruction  $\gamma_k \in \Gamma$  and  $t_{out}(\gamma_k)$  its ending time. The **time range membership function** of instruction  $\gamma_k$  with respect to class  $c_i \in C$  at time *t* is defined as:

$$[t,k,i] = \begin{cases} \langle k,i \rangle & \text{if } t_{in}(\gamma_k) \le t \le t_{out}(\gamma_k) \\ 0 & \text{otherwise} \end{cases}$$

(3.6)

where the values  $t_{in}(\gamma_k)$  and  $t_{out}(\gamma_k)$  are properties of the instruction  $\gamma_k$  with respect to a given execution trace  $\Gamma$ .

It is worth noting that the time range between  $t_{in}(\gamma_k)$  and  $t_{out}(\gamma_k)$  not only depends on the instruction latency but also includes the inter-instruction overhead resulting from stalls. When an instruction is stalled, in fact, it still occupies some resources. The time range membership function allows to know, at each clock cycle, which instructions are being executed.

Starting from the time range membership function it is possible to aggregate values in a perclass vision.

**Definition 5** The class load function represents the number of instructions belonging to class  $c_i$  being executed at time t. It is defined as:

$$\lceil t, i \rfloor = \sum_{k=1}^{N} \lceil t, k, i \rfloor$$

(3.7)

The class load function can be used to compute an instantaneous parallelism coefficient, defined as follows.

#### Definition 6 The instantaneous parallelism coefficient is defined as:

$$p_t = \begin{cases} 1/\sum_{i=1}^{|\mathcal{C}|} \lceil t, i \rfloor & \text{if } \sum_{i=1}^{|\mathcal{C}|} \lceil t, i \rfloor \neq 0\\ 0 & \text{otherwise} \end{cases}$$

(3.8)

where the summation extends to all classes in the taxonomy.

Figure 3.1 clarifies these concepts with an example in which three functional units  $U_1$ ,  $U_2$  and  $U_3$  execute eight instructions  $\gamma_1, \ldots, \gamma_8$  belonging to the classes  $c_1$ ,  $c_2$  and  $c_3$ . The figure is composed of two parts: the upper portion shows the scheduling of instructions on each unit while the lower portion reports the values of [t, i] and  $p_t$  for the considered scheduling.

| $U_1$ of             | $\gamma_4$ | $\in c_2$          | )      | $\gamma_6 \in c_3$ |                    | )      |                    | $\gamma_3 \in c_1$ |         |

|----------------------|------------|--------------------|--------|--------------------|--------------------|--------|--------------------|--------------------|---------|

|                      |            |                    |        | $\gamma_8 \in c_1$ |                    |        |                    | $\gamma_7$ (       | $E c_3$ |

| $U_2$                |            | o                  |        |                    | _                  | (      | >≺                 | >                  | O       |

| $U_3$ (              |            | $\gamma_1 \in c_1$ |        |                    | $\gamma_5 \in c_2$ |        | $\gamma_2 \in c_3$ |                    |         |

| $\lceil t,1 \rfloor$ | 1          | 2                  | 2      | 1                  | 1                  | 2      | 2                  | 2                  | 1       |

| $\lceil t,2 \rfloor$ | 1          | 1                  | 0      | 0                  | 1                  | 0      | 0                  | 0                  | 0       |

| $\lceil t,3  floor$  | 0          | 0                  | 1      | 1                  | 1                  | 0      | 0                  | 1                  | 1       |

| $p_t$                | 1/2        | 1/3                | 1/3    | 1/2                | 1/3                | 1/2    | 1/2                | 1/3                | 1/2     |

| t                    | 1          | 2                  | 3      | 4                  | 5                  | 6      | 7                  | 8                  | 9       |

|                      | Fi         | gure 3.            | 1: Exa | mple o             | f paral            | lelism | compu              | tation             |         |

Consider, for instance, the clock cycle at t = 3 and with instructions  $\gamma_6$ ,  $\gamma_8$  and  $\gamma_1$  being executed. The class load function  $\lceil 3,1 \rfloor$  is equal to 2 since  $\gamma_8, \gamma_1 \in c_1$ . Similarly,  $\lceil 3,3 \rfloor$  is equal to 1 since  $\gamma_6 \in c_3$  and  $\lceil 3,2 \rfloor$  is 0 since no instructions of class  $c_2$  are being executed. According to equation (3.8), the instantaneous parallelism coefficient  $p_3$  is equal to 1/(2+0+1) = 1/3. It can be proved that  $p_t \in [1/M; 1] \cup \{0\}$  with M being the maximum number of instruction that the specific architecture is capable of handling in the same clock cycle. As an example consider a simple DLX-like 5-stage pipeline architecture [12]: in this case M = 5 since, when the pipeline is full, all its stages are executing an instruction at every clock cycle. In more complex architectures, where more pipelines are present and possibly share some of the stages, the computation of M becomes more sophisticated since the observation of the status of the single units of all pipelines is necessary. The instantaneous parallelism coefficient  $p_t$  must then be aggregated according to the selected taxonomy in order to obtain a per-class vision of the amount of parallelism that the architecture under analysis can actually exploit. The following definition formalizes this concept.

**Definition 7** The *class parallelism coefficient* is a scale factor influencing the execution time of an instruction belonging to class  $c_i$  when executed in parallel with other instructions. It is modeled by the stochastic variable  $P_i$ , which is characterized by the density function:

$$f_{P_i}(x) = \frac{\sum_{t=0}^{\infty} \delta_{P_t=x} \lceil t, i \rfloor}{\sum_{t=0}^{\infty} \lceil t, i \rfloor}$$

(3.9)

where the summations actually extend only over all clock cycles needed for the execution of the trace  $\Gamma$ .

Referring again to the execution trace of figure 3.1, consider the density function  $f_{P_3}(x)$ . Since  $p_t \in \{1/3, 1/2\}$  and thus  $\delta_{p_t=x} = 1$  only when x = 1/3 or x = 1/2, then  $f_{P_3}(x)$  is to be computed only for such values. In particular for x = 1/3:

$$f_{P_3}(1/3) = \frac{\sum_{t=1}^{9} \delta_{p_t=1/3}[t,3]}{\sum_{t=1}^{9} [t,3]} = \frac{0+1+1+1}{0+0+1+1+1+0+0+1+1} = \frac{3}{5}$$

(3.10)

The same procedure leads to the result  $f_{P_3}(1/2) = 2/5$ . The parallelism coefficient p(s), similarly to the instruction overhead, can conveniently approximated with the expectation value of the stochastic variable  $P_i$ , that is:

$$p(s) = E[P_i] = \int_0^1 x \cdot f_{P_i}(x) dx \quad \text{with} \quad s \in c_i, \ x \in \mathbb{Q}$$

(3.11)

It must be noted that  $x \in \mathbb{Q}$  since it is computed as the ratio of two integer numbers and that  $0 \le x \le 1$  by definition, thus the integral is computed according to the Lebesgue's notion of measure. Concluding the example, p(s) for instructions in class  $c_3$  is:

$$p(s) = \frac{1}{2} \cdot f_{P_3}(1/2) + \frac{1}{3} \cdot f_{P_3}(1/3) = \frac{2}{5}$$

(3.12)

# 4 Methodology

This chapter presents the proposed methodology for the practical application of the model described in Chapter 3. After giving an overview of the flow in section 4.1, each section describes a methodology step, explaining also the reasons and previous literature that are behind the methodology design issues: section 4.2 presents the advantages and the motivation of a microcompiled approach; section 4.3 details the proposed simulation approach; section 4.4 shows the tuning activity to be performed to obtain statistical figures for class and instruction timing. Finally, section 4.5 explains the algorithm used to apply class figures to estimate the execution time of an arbitrary program.

# 4.1 Methodology Flow

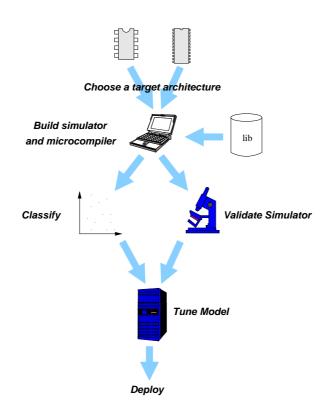

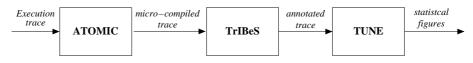

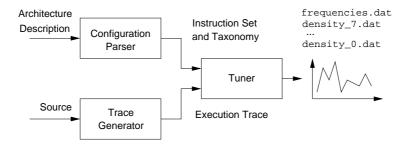

The proposed methodology consists in a series of activities that the model developer has to endure. These activities can be summarized as (see also figure 4.1):

- 1. Select a target processor architecture

- 2. Use the provided library (see Chapter 5) to build a behavioral simulator of the chosen architecture

- 3. Build a micro-compiler of the chosen instruction set

- 4. Possibly validate the simulator against a set of micro-benchmarks [13]

- 5. Develop the preferred classification, optionally using the developed simulator

- 6. Apply the tuning process to a series of benchmarks

- 7. Apply the model to the code

Each of these steps has an importance of its own, and it is detailed in the following.

First of all, the model developer has to focus on a target architecture: while the methodology is general, its application has to be restricted do a single architecture or a very narrow set of architectures. This is due to the fact that commercial architectures are extremely different between each other, and the design space for modern processors is also fairly large.

After choosing the target processor, as stated from definition 4, to apply the model the starting and ending instants of each instruction have to be known. The solution proposed here is to develop an architectural simulator that takes an assembly trace and annotates it by adding the starting and ending instants of each instruction. This simulator has a reference implementation that is discussed in Chapter 5. This simulator can be validated against a physical processor or against a validated simulator of the same architecture [8].

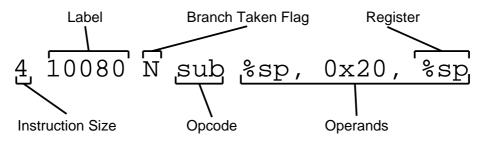

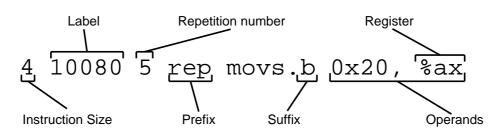

The provided library needs a micro-compiler to be built: this lets the simulator be as general as possible, without having to care about low-level assembly details. In fact, the microcompiler translates the architecture-specific assembly into an expanded, loosely encoded microinstruction set format called the *micro-code*. A library is provided to ease this task.

The instruction set has to be classified: this is done in order to reduce computational complexity (with a noticeable performance increase [2]), and to group instructions whose behavior is not known together with similar, but known, ones. The classification can be performed using the simulator to obtain figures for each instruction: this leads to a scatter diagram, where similar instructions tend to distribute in clusters. There are several statistical methods to obtain a supervised or non-supervised classification of data sets, among which we can cite clustering

Figure 4.1: Methodology flow for model application

algorithms, minimum deviation, maximum likelihood, K-means, etc [19]. The developer can choose the method he likes best or go through a manual classification. In either way, the reference implementation tools simplify remarkably this task.

Once the micro-compiler and classification have been defined, the model can be tuned by tracing a set of benchmarks: these are used to build the densities for every stochastic variable, i.e. overheads and coefficient parallelism. The data obtained can be used directly on newly produced code to obtain an accurate estimation of its execution time.

# 4.2 Micro-Compilation

This section details the reasons that brought to the choice of micro-compiling the assembly source before accepting it into the simulator. This has been done for some reasons:

- **Generality** By using a loosely encoded, internal micro-code, the simulator can be completely general and it can abstract from the target assembly.

- **Code reuse** The code developed for a specific architecture simulator may be used for others with similar characteristics. Also, the use of a unified assembly language for every simulator model pushes for the development of configurable and adaptable modules for different architectures.

- **Performance** The proposed general micro-code has a very small set of instructions with extremely simple behavior: it can be faster than real decode and execution.

For each instruction set architecture, a new micro-compiler has to be built. Anyway, this should be less expensive than renewing and developing the simulator from scratch for every target architecture. In addition, the tool chain provides libraries and macros provided in order to make the writing of a new compiler as simple as possible. The development of the micro-compiler requires some knowledge of the target architecture and instruction set: it is mandatory to know for each instruction which elements of the datapath are used and the corresponding latencies. These are not always available, but usually can be retrieved from assembly manuals and architecture datasheets. For micro-code details see Chapter 5, noticing that while its syntax is general, compilation is strictly bound to the structure of the simulated processor. This means that the micro-compiler has to be build *after* the simulator structure has been defined.

# 4.3 Behavioral Simulation

To obtain the data needed by the model, precise instruction performance figures has to be known. For the methodology to be effective, this data has to be retrieved in a fast and and simple way.

The simplest way to obtain the starting and ending cycle of each instruction, considering all the architectural details involved in the execution, is to use a simulator; RTL simulators represent an optimal choice as far as accuracy is concerned, but they significantly lack in speed. *Instruction Set Simulators* (ISSs) are another valid choice, since they are usually very accurate while running several orders of magnitude faster than RTL simulators. Various approaches have been proposed for ISS development; even these simulators are not particularly efficient, and are scarcely available for commercial systems: ISS are thus not a viable solution. Another possibility is to use a *performance simulator*, a simpler kind of simulator that considers the performance factors only [20]; these are often more available than ISSs, but anyway not easy to find for a given architecture and frequently lack of documentation. In addition, performance simulators are frequently less than cycle-accurate.

To solve such problems, an architectural simulator has been introduced: this is the meeting point between ISS and performance simulator in the sense that it provides nearly cycle accurate figures even if it avoids functional simulation. In practice, the proposed simulator models the architecture in its details under a performance-only point of view. instructions are processed into the various modules of the system only in the sense they are stored for the appropriate number of cycles. This performance simulation environment has to be highly customizable to fit any processor available and, in addition, it should to provide common modules to maximize code reuse and minimize development time.

## 4.3.1 Design Space Exploration

The simulation architecture should be able to consider every aspect of modern processors design space. In this way, even newly produced processors can be simulated without having to rewrite the core simulation code. Such design space is extremely large, but for performance analysis it restricts to a few fields of interest:

- Pipelining

- Branch Prediction Techniques

- Instruction Level Parallelism

- Memory access

To cover the design space in each of these fields, two possible solutions are viable: simulate the system at a lower level with respect to these (e.g. functional units that handle bitstreams instead of instructions) or to develop a modular system whose modules hold enough degrees of freedom. The former solution may result too complex, hence the latter was chosen.

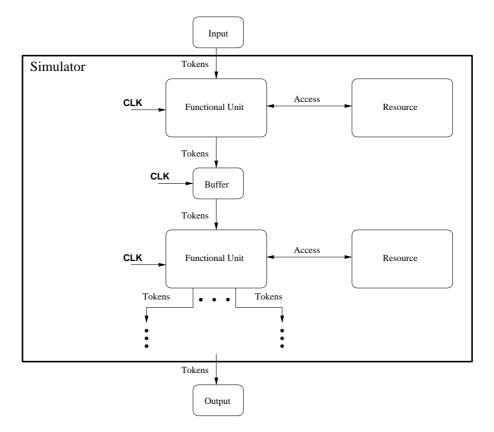

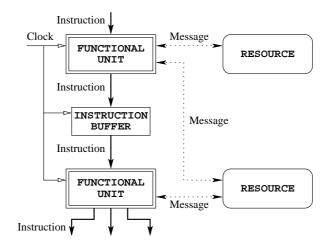

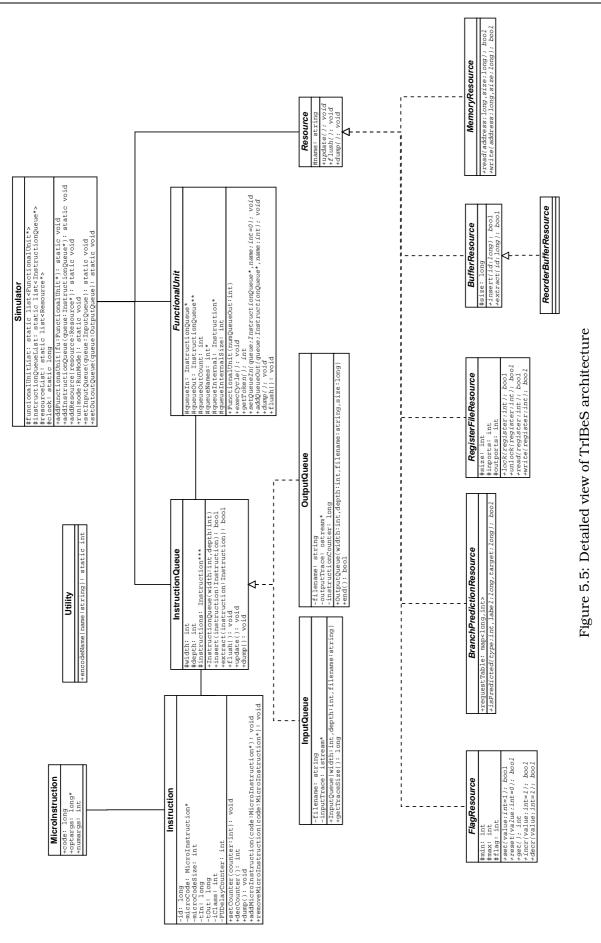

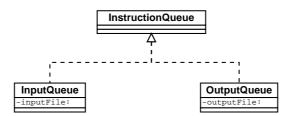

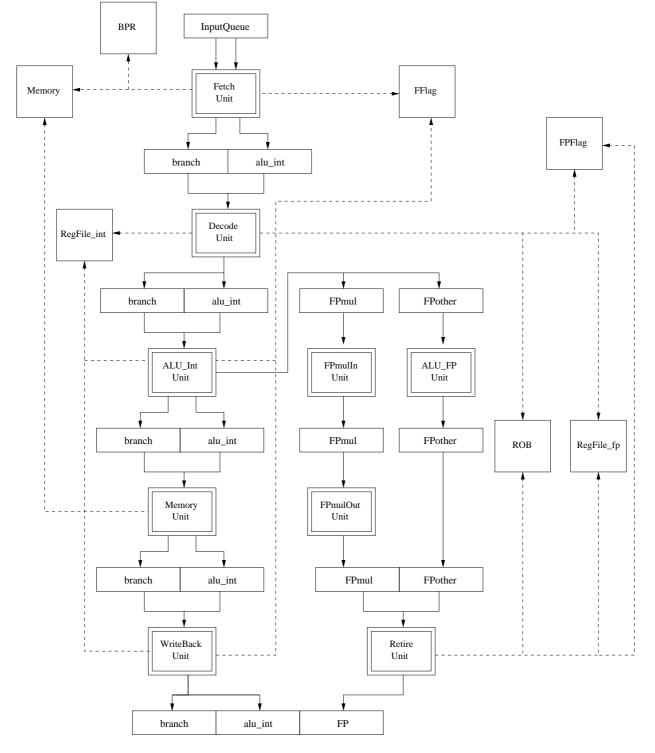

To gain degrees of freedom, it has been chosen that the simulator would work on an *abstraction* of processor architecture: each system is seen as a set of *functional units* that communicate

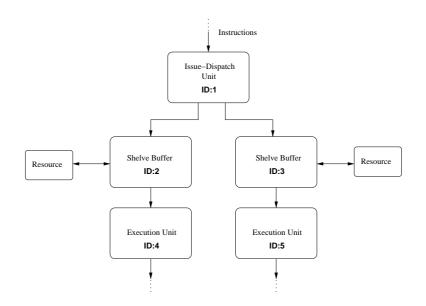

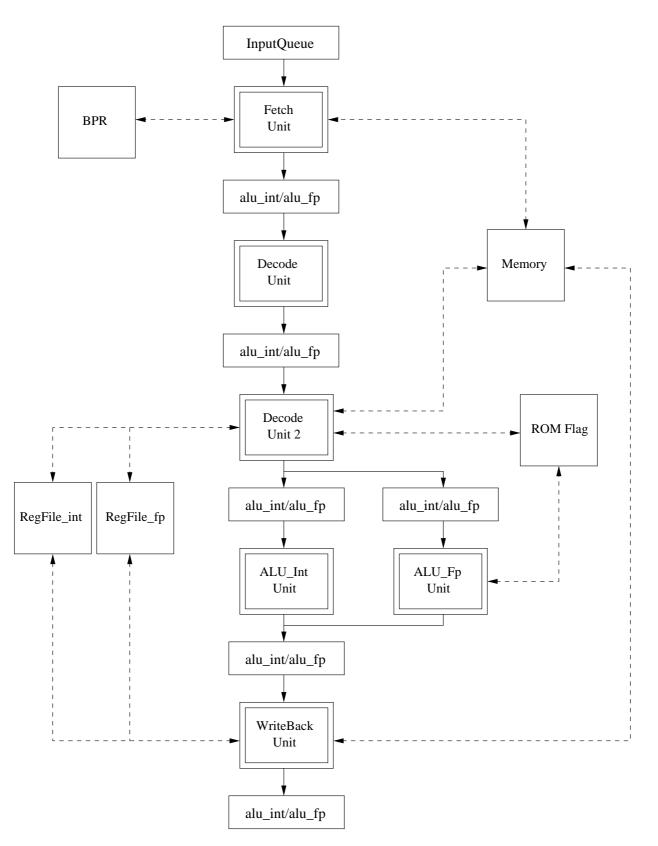

Figure 4.2: Proposed simulator architecture

with each other by exchanging *tokens*. Each functional unit may also have to access *resources* in order to process a token, and resources can grant or refuse access by a given unit. All of these elements work concurrently in a discrete time environment, where the unit time interval is represented by the clock cycle.

As figure 4.2 shows, functional units are exchange tokens via buffers that are used to hold tokens until the next clock cycle: this means that the simulator is strictly synchronous. This last choice makes the modeling of asynchronous circuits impossible, but this can be considered a good trade-off since asynchronous systems have very scarce diffusion.

In the following, some examples on how this structure can fit on the design space of ILP, Pipelining and Memory Access are presented.

### 4.3.1.1 Pipelining

Pipelining has been introduced in micro-processors starting from the end of the 1960s as an effective floating point number crunching technique [25]. With pipelining, a number of functional units are employed in sequence to perform a single computation. These units form an assembly line or pipeline: each unit performs a certain stage of the computation and each computation goes through the pipeline. Pipelining fits perfectly in the model, as can be seen directly from figure 4.2. From this starting point, many other techniques are used to increment processor performance, and thus extend the design space associate to modern architectures.

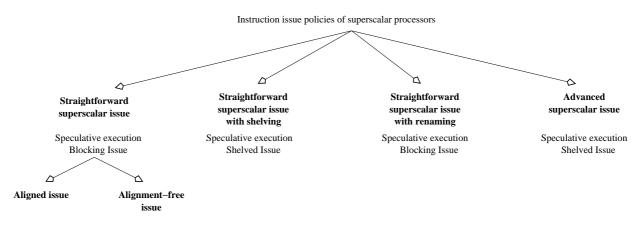

To exploit potential instruction parallelism (due to independent instructions) at its maximum, superscalar processors have been introduced. Such processors can process more than one instruction per clock cycle. These are the main focus of this work, since superscalarity and aggressive ILP are the key issues of today's processor design.

Figure 4.3: Instruction issue design space for superscalar processors

### 4.3.1.2 Superscalarity

While considering superscalarity, it is important to assure that the proposed simulation model can deal with:

- Superscalar Issue

- Alignment

- Shelving/Dispatching

- Register Renaming/Forwarding

- Parallel Execution

- Preservation of sequential integrity

Superscalar issue is a complex field, and involves techniques such as the alignment of instructions, forwarding and register renaming.

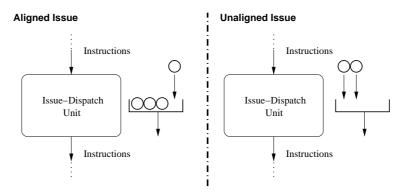

There are two types of instruction alignment: aligned issue, instructions are issued in groups only when there is a sufficient number of instructions to fill the group, and unaligned issue, instructions are issued when available. In both cases, the functional unit representing the issue stage of the pipeline models this behavior: for aligned issue it waits until it is full of tokens, for unaligned issue it fires tokens as they arrive (see figure 4.4). This means that each unit has an *internal queue* with variable width: this queue is used to hold tokens inside the functional unit until their processing is finished. The size of such queue can be defined as a parameter of the unit.

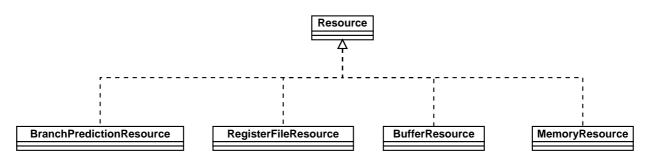

Issue alignment has to be combined with dispatching techniques: there is usually one or more functional unit whose job is to distribute instructions to different execution units. This is modeled using multiple functional units that are connected to a single source. The most popular way of detecting instruction dependencies in superscalar execution is the use of *shelving buffers*, i.e. buffers that hold instructions before they are passed to the execution stage until all dependencies are satisfied. Dependencies are checked by communication with resources and by special flag bits associated to the buffer. Shelving buffers can be *distributed* (exactly one buffer for execution unit), *partially distributed* or *centralized* if they also behave like dispatching units (by being bound to more than one execution unit). Such considerations lead to the consequence that each functional unit can be bound to many other functional units; a functional unit has to know which one it is sending instructions to, so it is mandatory to associate a *unique identifier* to functional units. In addition, dependency check is done by resource access, as figure 4.5 shows.

Figure 4.5: Shelving buffer model, considering distributed shelving

Register renaming and forwarding are two common (the latter a bit obsolete) means of avoiding data dependencies between instructions. The former uses a number of physical registers, on which the logical (the accessible ones) are mapped on, the latter forwards operation results from a set of pipeline stages (i.e. memory access and execute) to the preceding one on certain conditions. These approaches can be modeled with resources: a resource behaving as a register file can include all the logic pertaining register renaming while a resource flag can be raised if forwarding is not possible, and thus requiring a stall.

Finally, parallel execution and the preservation of sequential integrity have to be considered. Parallel execution is the simplest: all functional units work concurrently as stated before, this means that the core simulator architecture is sufficient to model a set of concurrent operations. The presence of concurrent operations implies, as a logical consequence, an enhancement of instruction throughput, *out-of-order execution*: instructions are executed whenever resources are available, possibly in an order that differs from the one in which they were fetched. While this is no modeling problem, it means that sequential integrity preservation techniques have to be introduced.

The preservation of sequential integrity is usually obtained by the use of *reorder buffers*, special buffers that act as circular registers, returning only the oldest instruction when requested. In this way, instructions are retired (i.e. exit) from the processor only in sequential order. Reorder Buffers are modeled with resources, their size defined as a parameter.

As shown, all of these approaches can be modeled with the proposed simulation architecture: all the logic pertaining to the various ILP characteristics of a target processor is hidden inside functional unit and resource code. In conclusion, the main simulator characteristics are:

- The simulator is made by Functional Units, Resources and Buffers.

- Each functional unit has only one input, but it may have many outputs

- Each functional unit has a variable-sized internal instruction queue

- A functional unit is identified by a unique ID, known also by other linked functional units

- All functional units act concurrently

These characteristics appear in the reference implementation, as described in detail in Chapter 5.

### 4.3.1.3 CISC over RISC

In today's processors, it is not infrequent to find CISC processor implementations built over RISC cores. These systems have specific units destined to the decoding of CISC instructions into RISC ones. This is more difficult to model with the proposed structure, but it is still possible: the decode units may output more tokens than they receive as input. In this way there is the added ability of *token generation*: in practice, the simulator decode units act exactly as their physical counterparts, by issuing a set (i. e. one or more) of micro-instructions for every one processed. However, since all the interest is put on performance simulation, this behavior is not mandatory. In some architectures, decoding and execution over a RISC core may be modeled considering CISC instructions only, looking at the RISC core as a black box, maintaining accuracy. As an example, an architecture where RISC instructions have all the same latency could be modeled with a CISC-only solution, with instructions having variable latency.

### 4.3.2 Simulation algorithm

Now that all the modules of the simulator are defined, the simulation algorithm can be specified. Such algorithm can be described using pseudo-code:

#### **Algorithm 1** Simulation of a clock cycle

```

1: sort_functional_units();

2: for all functional units do

3: execute_cycle();

4: end for

5: for all buffers do

6: update();

7: end for

8: for all resources do

9: update();

10: end for

```

As the code clearly shows, the algorithm is made by a set of sequential steps:

- 1. To avoid access conflicts on resources, concurrent access is granted only to the oldest instruction: functional units are sorted according to the *age* of the instructions they contain, from oldest to youngest (line 1)

- 2. Each functional unit executes a cycle in the given order (lines 2 to 4)

- 3. Each instruction buffer is updated: instructions are moved from master to slave entry, so they can be accessed from the next functional units in the following cycle (lines 5–7)

- 4. Eventually, resources are updated. It is worth noting that this step is optional, since resources may be clock-independent (lines 8–10)

The simulation iteration is repeated for the number of clock cycles needed to execute the chosen benchmark.

## 4.4 Tuning

The tuning process is a straight application of the model presented in Chapter 3. The available timing information, due to simulation, is aggregated in density functions: delays and parallelism coefficients are computed (by application of the corresponding formulae) for each class, their values summed and normalized. The result is a set of matrices that represent delay and parallelism coefficients density functions. The expectation value of these functions is then computed and stored, completing the model tuning. The algorithm describing the tuning process follows:

**Algorithm 2** Tuning of the model given a sample trace

| 1:  | clock := 0;                                                                 |

|-----|-----------------------------------------------------------------------------|

| 2:  | V := empty vector of instructions $s$ ;                                     |